Install Steam

login

|

language

简体中文 (Simplified Chinese)

繁體中文 (Traditional Chinese)

日本語 (Japanese)

한국어 (Korean)

ไทย (Thai)

Български (Bulgarian)

Čeština (Czech)

Dansk (Danish)

Deutsch (German)

Español - España (Spanish - Spain)

Español - Latinoamérica (Spanish - Latin America)

Ελληνικά (Greek)

Français (French)

Italiano (Italian)

Bahasa Indonesia (Indonesian)

Magyar (Hungarian)

Nederlands (Dutch)

Norsk (Norwegian)

Polski (Polish)

Português (Portuguese - Portugal)

Português - Brasil (Portuguese - Brazil)

Română (Romanian)

Русский (Russian)

Suomi (Finnish)

Svenska (Swedish)

Türkçe (Turkish)

Tiếng Việt (Vietnamese)

Українська (Ukrainian)

Report a translation problem

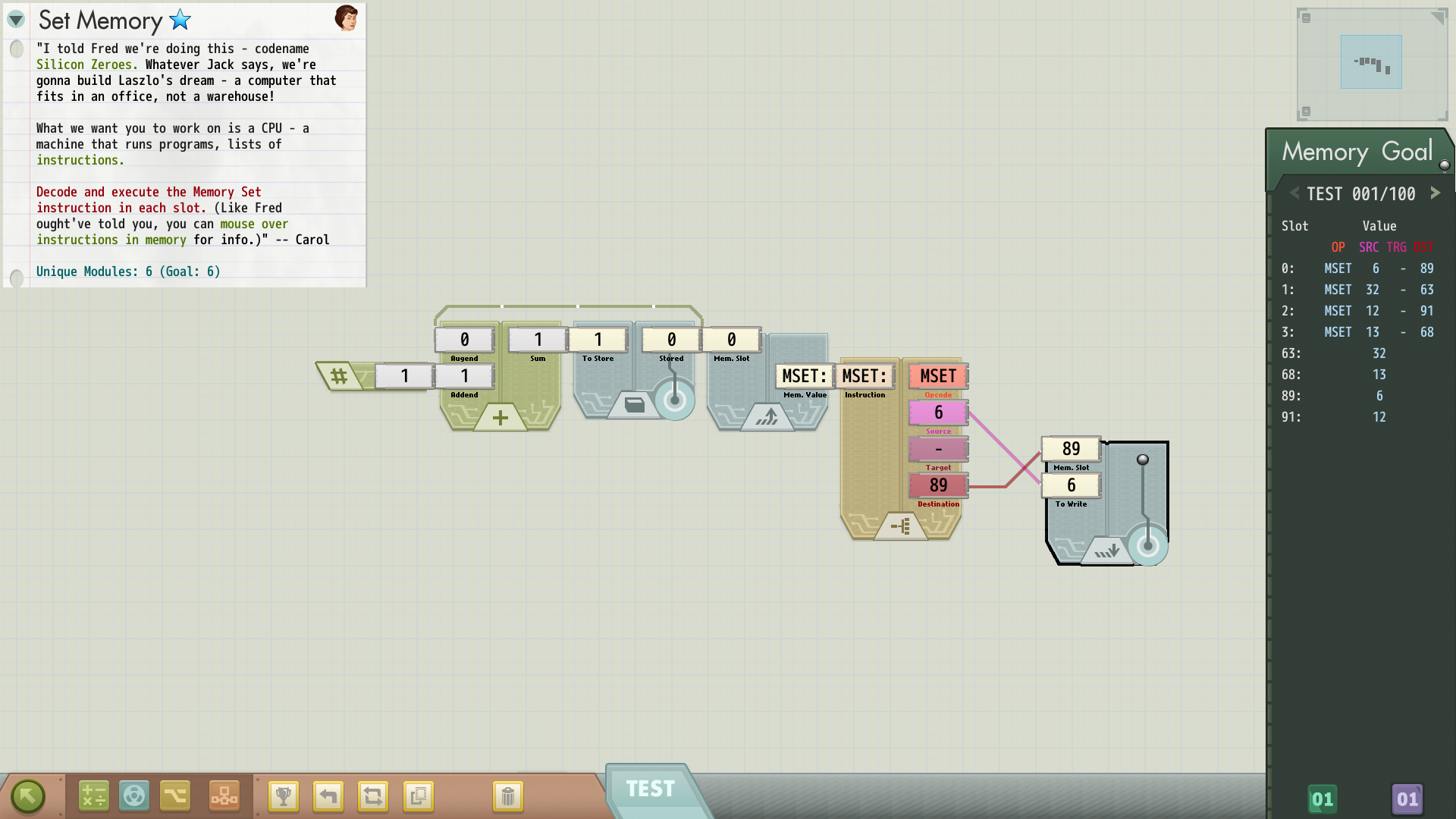

DELAY CPU

这个是完全按照你的连的

演示

这个是我稍微改了一下的,就当给你提了个pr,hhhhh。

演示

Part 3/3 (一次只能1000字)

// Modules definition

module Adder(output Sum, input Augend, Addend); endmodule

module Equals(output Output, input Base, Comparator, ...); endmodule

module Input_Selector(output Output, input Input_Select, Input_0, ...); endmodule

module Latch(output Store, input To_Store); endmodule

module Number(output Value, input Const_Number); endmodule

module Reader(output Mem_Value, input Mem_Slot); endmodule

module Writer(input Mem_Slot, To_Write); endmodule

Part 2/3 (一次只能1000字)

Equals e_c(p_eq, p_data_b, p_n); // Equals 1 -> port #eq : if n == b

Latch l_eq(p_rst, p_eq), // Latch 2 -> port #rst : reset n = 1, s = a after eq signal

l_n(p_n, p_next_n), // Latch 3 -> port #n : n times repeated

l_s(p_s, p_next_s); // Latch 4 -> port #s : s = a * (n - 1)

Adder a_addr_n(p_n_1, p_n, p_1), // Adder 3 -> port #n_1 : n + 1

a_addr_s(p_s_1, p_s, p_data_a); // Adder 4 -> port #s_1 : s + a, or a * n

Input_Selector sel_c(p_sel_c, p_eq, -, p_c), // I-Sel 1 -> port #sel_c

sel_n(p_next_n, p_rst, p_n_1, p_1), // I-Sel 2 -> port #next_n

sel_s(p_next_s, p_rst, p_s_1, p_data_b); // I-Sel 3 -> port #next_s

Writer w_c(p_sel_c, p_s_1); // Writer 1 : save data[c] = s_1 if n == b

endmodule

Part 1/3 (一次只能1000字)

17组件过(目标18) ,不能贴图,就用Verilog写了,四个Latch令人头秃...

// Solution for Multiply

// @author: Dorence Deng

module Solution();

wire p_1, p_a, p_b, p_c, p_next_addr, p_data_a, p_data_b, p_sel_c,

p_eq, p_rst, p_n, p_s, p_n_1, p_s_1, p_next_n, p_next_n; // wire p_x == port #x

Number num1(p_1, 1); // Number 1 -> port #1

// to calculate a * b = c, repeat adding a for b times

Latch l_a(p_a, p_next_addr); // Latch 1 -> port #a : address of a

Adder a_addr_b(p_b, p_a, p_1), // Adder 1 -> port #b : address of b

a_addr_c(p_c, p_b, p_1), // Adder 2 -> port #c : address of c

a_next_addr(p_next_addr, p_sel_c, p_1); // Adder 3 -> port #next_addr

Reader r_a(p_data_a, p_a), // Reader 1 -> port #data_a : value of a

r_b(p_data_b, p_b); // Reader 2 -> port #data_b : value of b